從零開始制作屬于你自己的GPU:基于FPGA的圖形加速器實(shí)現(xiàn)原理

一�、引言

在現(xiàn)代計(jì)算機(jī)系統(tǒng)中���,圖形處理單元(GPU)扮演著至關(guān)重要的角色。它們不僅在游戲和圖形渲染中發(fā)揮著核心作用����,還在深度學(xué)習(xí)��、數(shù)據(jù)分析等領(lǐng)域展現(xiàn)出巨大潛力。然而���,市面上的GPU往往價(jià)格不菲,且難以滿足所有定制化需求。因此���,從零開始制作一個(gè)屬于你自己的GPU�����,基于現(xiàn)場(chǎng)可編程門陣列(FPGA)來實(shí)現(xiàn)圖形加速器�,成為了一個(gè)既實(shí)用又具有挑戰(zhàn)性的選擇��。

二、硬件設(shè)計(jì)基礎(chǔ)

2.1 FPGA選型

選擇合適的FPGA是項(xiàng)目成功的關(guān)鍵����。你需要考慮FPGA的邏輯單元數(shù)量����、內(nèi)存大小��、I/O接口數(shù)量以及價(jià)格等因素���。對(duì)于初學(xué)者來說�����,一款中等規(guī)模的FPGA��,如Xilinx的Zynq-7000系列或Intel的Cyclone系列,都是不錯(cuò)的選擇����。

2.2 開發(fā)板準(zhǔn)備

購買與所選FPGA相匹配的開發(fā)板��。開發(fā)板上通常包含了FPGA芯片��、電源管理���、時(shí)鐘源、存儲(chǔ)器接口以及各種外設(shè)接口(如HDMI�、SD卡��、UART等)。確保開發(fā)板上的資源能夠滿足你的項(xiàng)目需求���。

2.3 硬件連接設(shè)計(jì)

根據(jù)你的GPU設(shè)計(jì)需求�,規(guī)劃并連接必要的硬件接口�����。例如����,如果你打算實(shí)現(xiàn)一個(gè)支持高清視頻輸出的GPU�,那么你需要確保開發(fā)板上具有HDMI接口,并設(shè)計(jì)相應(yīng)的電路來連接FPGA和HDMI接口�。

三�����、Verilog編程實(shí)現(xiàn)

3.1 圖形加速器架構(gòu)設(shè)計(jì)

在Verilog編程之前�,你需要先設(shè)計(jì)圖形加速器的整體架構(gòu)��。這通常包括像素處理單元、紋理映射單元�、光柵化單元等關(guān)鍵組件���。每個(gè)組件都需要實(shí)現(xiàn)特定的功能��,并與其他組件協(xié)同工作����。

3.2 Verilog模塊編寫

根據(jù)架構(gòu)設(shè)計(jì)��,開始編寫各個(gè)模塊的Verilog代碼。例如����,像素處理單元可能需要對(duì)輸入的像素?cái)?shù)據(jù)進(jìn)行顏色空間轉(zhuǎn)換���、亮度調(diào)整等操作;紋理映射單元?jiǎng)t需要實(shí)現(xiàn)紋理采樣和過濾等功能���。

3.3 模塊集成與測(cè)試

將所有模塊集成到一起�����,形成一個(gè)完整的圖形加速器。在集成過程中���,確保各個(gè)模塊之間的接口和數(shù)據(jù)流是正確的���。然后�����,使用仿真工具對(duì)圖形加速器進(jìn)行功能仿真�,驗(yàn)證其是否滿足設(shè)計(jì)要求。

四��、系統(tǒng)集成與調(diào)試

4.1 FPGA配置與下載

將編寫好的Verilog代碼綜合成比特流文件,并下載到FPGA開發(fā)板上��。這通常需要使用FPGA廠商提供的開發(fā)工具(如Xilinx的Vivado或Intel的Quartus)。

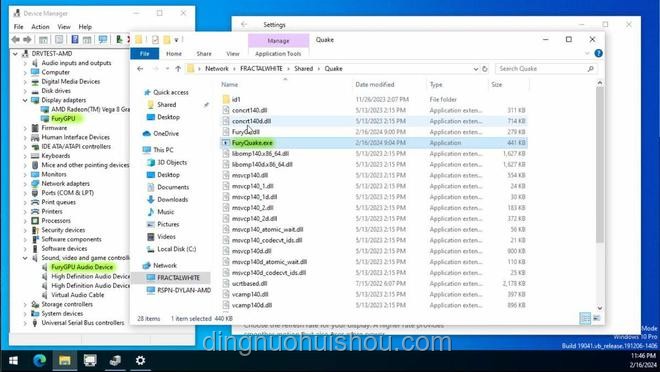

4.2 操作系統(tǒng)與驅(qū)動(dòng)開發(fā)

如果你的圖形加速器需要與操作系統(tǒng)交互��,那么你需要開發(fā)相應(yīng)的驅(qū)動(dòng)程序�����。驅(qū)動(dòng)程序負(fù)責(zé)將應(yīng)用程序的圖形渲染請(qǐng)求傳遞給圖形加速器��,并處理加速器的響應(yīng)�����。

4.3 系統(tǒng)調(diào)試與優(yōu)化

在實(shí)際運(yùn)行過程中,你可能會(huì)遇到各種問題��。這時(shí)�����,你需要使用調(diào)試工具(如邏輯分析儀、示波器等)來定位問題所在���,并進(jìn)行相應(yīng)的優(yōu)化。優(yōu)化可能包括調(diào)整硬件設(shè)計(jì)���、改進(jìn)Verilog代碼����、優(yōu)化驅(qū)動(dòng)程序等���。

五���、實(shí)用技巧和竅門

3 條評(píng)論